集成电路(Integrated Circuit, IC)引脚图是电子工程与集成电路设计中至关重要的文档,它直观展示了芯片外部引脚(Pin)的物理排列、编号、功能定义及电气特性。对于电路设计工程师、硬件开发人员和电子爱好者而言,准确理解和应用引脚图是成功实现电路功能、确保系统可靠性的第一步。本文将围绕集成电路引脚图的基础知识、设计考量及其在实际应用中的关键作用进行阐述。

一、 引脚图的核心要素

一张标准的集成电路引脚图通常包含以下核心信息:

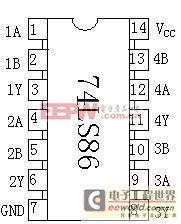

- 引脚编号与排列:明确标识每个引脚的唯一编号。常见的编号方式有逆时针顺序(多见于双列直插封装DIP)或矩阵坐标式(多见于球栅阵列封装BGA)。芯片上通常有一个凹槽、圆点或斜角作为引脚1的标识。

- 引脚名称/功能:每个引脚都有其特定的功能缩写,如VCC/VDD(电源正极)、GND/VSS(电源地)、CLK(时钟)、IN/OUT(输入/输出)、EN(使能)等。同一引脚可能具备复用功能。

- 电气类型:标明引脚是电源、地、数字输入/输出、模拟输入/输出、漏极开路(Open Drain)或双向(Bidirectional)等,这直接关系到外部电路的设计。

- 关键注释:包括推荐的去耦电容位置、未连接引脚(NC)的处理方式、以及绝对最大额定值(如耐压)等警告信息。

二、 引脚图背后的集成电路设计考量

引脚布局并非随意安排,而是芯片设计阶段深思熟虑的结果,主要受以下因素驱动:

- 信号完整性:高速或敏感信号(如时钟、模拟输入)的引脚需远离噪声源(如电源、数字输出),并可能被地线引脚包围以提供屏蔽。电源和地引脚通常会被成对或多重布置,以降低阻抗和环路电感。

- 功耗与散热:大电流的电源和地引脚需要有足够的数量和合理的布局,以减少电压降和发热。有时功率引脚会安排在芯片中心或特定位置以优化散热路径。

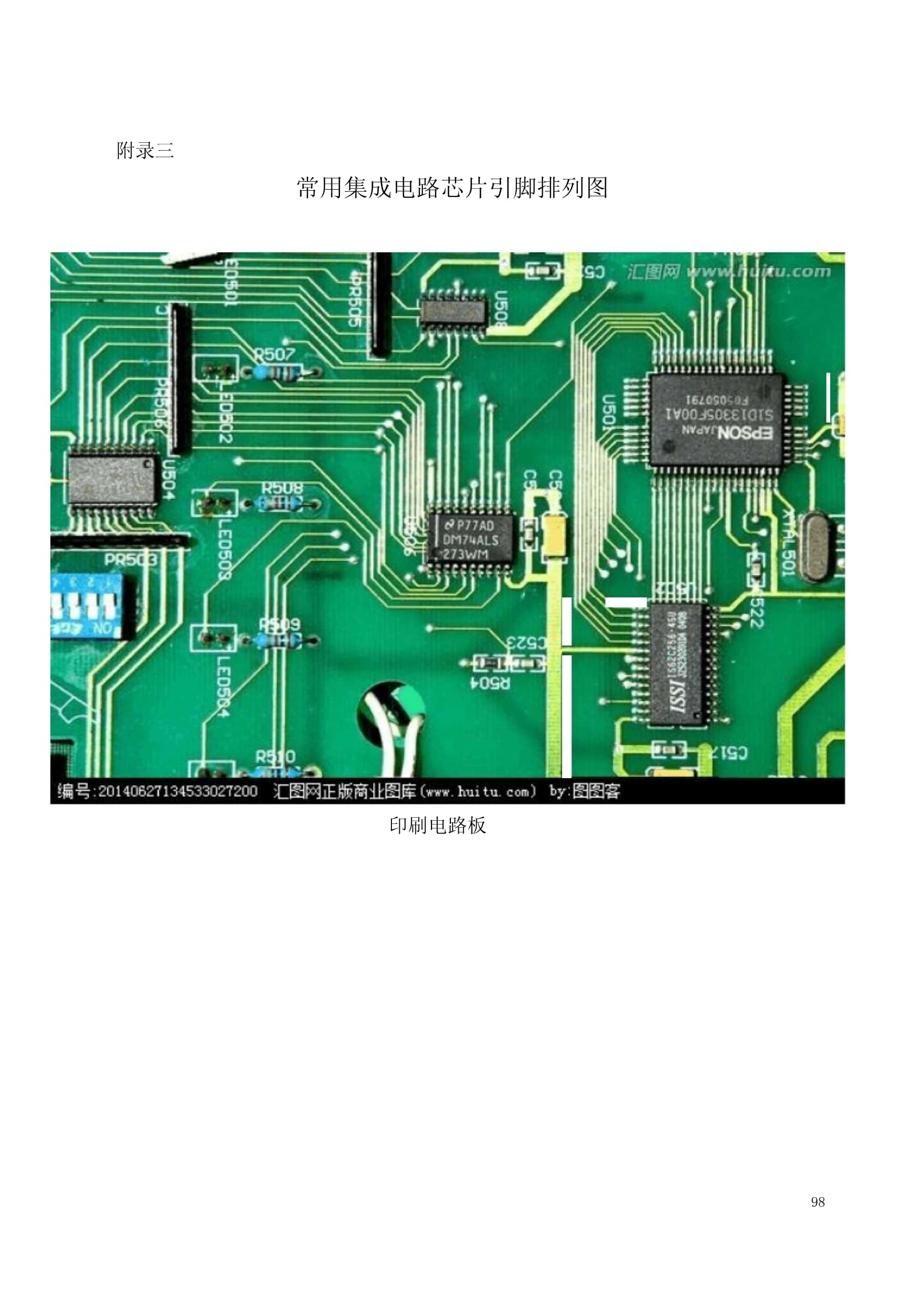

- 封装与制造工艺:引脚的物理排列必须符合封装技术(如QFP、BGA、QFN)的约束。设计需考虑邦定(Bonding)线长度、寄生参数最小化以及与PCB(印制电路板)布线难度之间的平衡。

- 功能分组与易用性:将相关功能的引脚(如同一总线、同一外设接口)集中排列,可以极大简化外围电路设计和PCB布线。

- 测试与调试:设计中常会预留专用的测试引脚,或使关键信号易于在外部探测,以方便生产测试和系统调试。

三、 在实际电路设计中的应用要点

工程师在根据引脚图进行电路设计和PCB布局时,应重点关注:

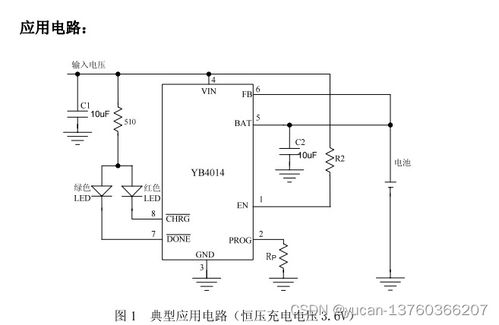

- 严格遵循数据手册:务必以芯片制造商提供的最新官方数据手册(Datasheet)中的引脚图为唯一权威依据。示意图中的“典型应用电路”极具参考价值。

- 电源完整性设计:在PCB上,必须在靠近芯片的电源与地引脚之间放置高质量的去耦电容(通常为一大一小容值并联),以滤除高频噪声并为芯片瞬间电流需求提供本地储能。

- 未连接引脚的处理:对于标记为“NC”或未定义功能的引脚,通常建议将其悬空或不连接。但有些芯片可能要求将未使用的输入引脚上拉或下拉至固定电平,以防止其浮空导致功耗增加或不稳定,需仔细阅读说明。

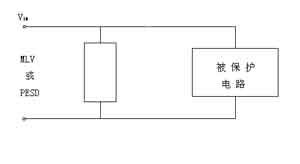

- ESD与过载保护:对于连接到外界的引脚(如通信接口、按键输入),应根据需要添加串联电阻、TVS管或滤波电路,提供静电放电(ESD)和过压过流保护。

- 利用评估板与参考设计:对于复杂芯片,制造商提供的评估板(Eval Board)原理图和PCB布局是最佳的学习范本,它直观展示了官方推荐的引脚连接、外围元件选型和布局布线方案。

###

集成电路引脚图是连接芯片内部复杂硅片设计与外部真实世界应用的桥梁。它不仅仅是一张接线图,更凝聚了芯片设计者对信号、电源、散热和可制造性的综合权衡。熟练掌握引脚图的解读与应用,是每一位硬件工程师构建稳定、高效电子系统的基本功。从读懂每一个符号开始,方能精准驾驭芯片的强大功能,将创新的电路设计变为现实。