在集成电路(IC)设计与半导体制造领域,静电放电(ESD)保护是确保芯片可靠性的关键环节。其中,栅极接地NMOS(Gate-Grounded NMOS, GGNMOS)因其结构简单、兼容标准CMOS工艺等优点,被广泛用作片上ESD保护器件。GGNMOS在实际应用中常面临一个经典挑战——"溃通"(或译作"穿通", Punch-Through)问题。这一问题在各大电路设计论坛(如EETOP、创芯网论坛等)及数字/模拟设计社区中,一直是工程师们关注和讨论的焦点。

一、GGNMOS溃通问题的机理

GGNMOS作为ESD保护器件,其核心工作原理在于在ESD事件的高压瞬态冲击下,通过触发寄生NPN双极晶体管(由源极、P型衬底和漏极构成)进入雪崩击穿与 snapback(回滞)状态,从而泄放大电流。当器件尺寸持续微缩至深亚微米乃至纳米节点时,沟道长度变短,漏极与源极之间的耗尽区更容易在高压下连通。

所谓"溃通",是指在栅极电压为零(接地)的正常关断状态下,由于漏极电压过高,导致漏结的耗尽区横向扩展至与源结耗尽区相连,从而在源漏之间形成一条不受栅压控制的导电通道。此时,器件在远低于雪崩击穿电压的条件下就发生了显著的漏电流,其I-V特性曲线上的维持电压(Vh)会显著降低,甚至可能消失。

二、溃通对ESD保护性能的影响

- 过早触发与保护失效:溃通导致GGNMOS在较低的ESD电压下就提前导通,但其泄放能力可能不足。这会使本应由GGNMOS保护的核心电路过早承受ESD应力,增加失效风险。

- 维持电压过低:理想的ESD保护器件在触发后应有一个足够高的维持电压,以确保在系统正常上电期间(如电源轨波动)不会误触发。溃通使Vh降低,可能引发闩锁(Latch-up)或系统级功能异常。

- 电流泄放能力下降与局部热失效:溃通过程形成的导电通道可能不均匀,导致电流集中,引起局部过热和二次击穿,反而降低了器件的整体ESD鲁棒性(如HBM/CDM等级)。

三、电路设计论坛中的常见讨论与解决方案

在EETOP、创芯网等专业论坛上,针对GGNMOS溃通问题的讨论与实践经验非常丰富,主要集中在工艺与设计协同优化方面:

- 器件结构调整:

- 增加沟道长度:这是最直接的方法,但会增大面积并可能影响响应速度。

- 采用轻掺杂漏(LDD)或 HALO(晕环)注入:优化漏端掺杂剖面,抑制耗尽区过度扩展,增强抗溃通能力。这是工艺层面常用的解决方案。

- 电路级改进:

- 串联电阻或二极管:在GGNMOS的栅极或源极路径串联电阻,或与二极管串联/并联使用,以调整触发特性,但需权衡面积与速度。

- 采用可控硅(SCR)或堆叠(Stacked)GGNMOS:对于高压或先进节点,SCR结构能提供更高的单位面积ESD性能。堆叠GGNMOS则能有效分摊电压,避免单管承受过高电压而溃通。

- 仿真与模型验证:

- 工程师们强调利用TCAD工具进行器件级仿真,直观分析电场分布与电流路径。

- 结合Foundry提供的经过ESD特性校准的紧凑模型(如BSIM),在电路仿真中预评估溃通风险,并优化器件尺寸(W/L)、布局(如叉指结构)和驱动条件。

四、跨领域视角:数字、模拟与嵌入式设计的考量

溃通问题的影响因应用领域而异:

- 数字电路:更关注GGNMOS在电源轨(VDD-VSS)间的保护,溃通可能导致系统级上电浪涌误触发,需仔细评估维持电压与电源电压的裕量。

- 模拟/射频电路:对寄生电容和漏电流极其敏感。溃通引入的额外漏电和电容变化可能恶化增益、噪声等关键指标,设计时需在ESD鲁棒性与性能间取得精细平衡。

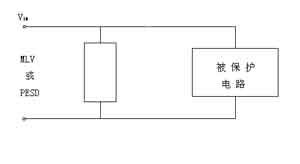

- 嵌入式与微电子系统:在系统级封装(SiP)或板级设计中,GGNMOS需与片外保护元件协同工作。理解其溃通特性有助于制定更有效的分级保护策略。

###

GGNMOS的溃通问题是深亚微米以下IC设计中一个不可忽视的可靠性挑战。它深刻体现了半导体物理、工艺制程与电路设计的紧密耦合。持续参与EETOP、创芯网等专业论坛的交流,跟踪业界最新解决方案(如FinFET工艺下的ESD设计新范式),对于电子工程师、IC设计人员及微电子专业学生而言,是提升设计能力、规避设计风险的重要途径。通过深入理解机理并灵活运用设计技巧,方能在追求高性能、高可靠性的集成电路设计之路上行稳致远。