在当今高度信息化的时代,半导体集成电路(IC)作为电子设备的核心,其复杂性与集成度日益提升。为了在研发、生产与应用中有效区分和管理数以万计的芯片,一套系统而规范的型号命名法应运而生,并与集成电路设计流程紧密关联,共同构成了半导体产业的技术基石。

一、集成电路型号命名法:解码芯片的“身份证”

集成电路的型号如同其独一无二的“身份证”,通常由字母和数字组合而成,遵循一定的命名规则,以传达关键信息。不同厂商虽有各自体系,但大体包含以下核心要素:

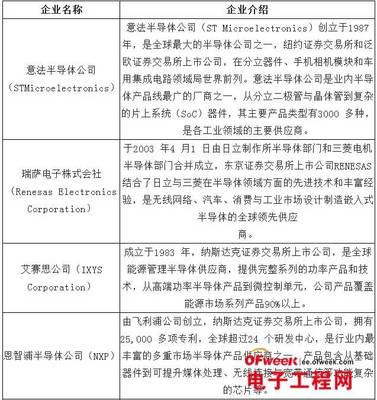

- 厂商前缀:标识芯片制造商,如Intel的“IN”、Texas Instruments的“SN”或“TL”、STMicroelectronics的“ST”。

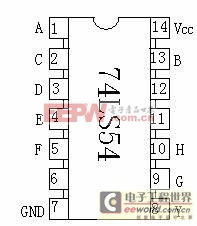

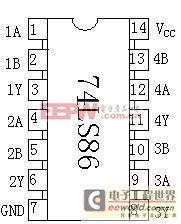

- 系列/功能代码:指明芯片的类别或主要功能,例如“74”代表通用TTL逻辑系列,“LM”表示线性放大器(如运算放大器),“MAX”常为Maxim公司的模拟信号处理芯片。

- 型号序号:同一系列中区分具体型号的数字,定义了芯片的详细功能与性能参数,如“7400”是四路2输入与非门,“LM358”是双运算放大器。

- 性能/规格后缀:进一步描述工作温度范围、封装形式、速度等级等。例如,“C”代表商业温度范围(0°C至70°C),“M”代表军用温度范围(-55°C至125°C),“N”可能代表塑料双列直插封装(PDIP)。

示例解析:型号“SN74HC00N”可解读为:德州仪器(SN)生产的74系列高速CMOS(HC)逻辑芯片中的四路2输入与非门(00),采用塑料双列直插封装(N)。

这套命名法不仅方便了工程师的选型与采购,也反映了芯片的技术代际、工艺特点和市场定位,是连接设计、制造与应用的重要桥梁。

二、集成电路设计:从构思到实现的精密之旅

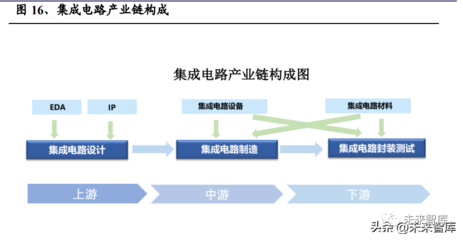

集成电路设计是将系统需求、电路功能转化为可在硅片上实现的物理版图的复杂过程。它通常遵循一个分层化、迭代化的设计流程,主要阶段包括:

1. 系统架构设计:

定义芯片的整体功能、性能指标(如速度、功耗、面积)和系统级模块划分。这需要综合考虑应用场景、算法需求和工艺制程的约束。

- 前端设计(逻辑设计):

- 功能描述:使用硬件描述语言(HDL),如Verilog或VHDL,编写寄存器传输级(RTL)代码,精确描述芯片各模块的逻辑功能与时序行为。

- 功能验证:通过仿真工具,验证RTL代码是否满足设计规范,确保逻辑正确性。这是发现和修正错误的关键阶段。

- 逻辑综合:利用综合工具,将RTL代码映射到目标工艺库的标准逻辑单元(如与门、或门、触发器等),生成门级网表。此过程会进行时序、面积和功耗的初步优化。

- 后端设计(物理设计):

- 布局规划:确定芯片核心区域、各个功能模块的摆放位置以及电源/地线网络的全局规划。

- 布图与布线:将综合后的门级网表中的所有标准单元和宏模块进行精确摆放(布局),并完成它们之间的所有电气连接(布线)。

- 时序收敛与物理验证:进行详细的静态时序分析(STA),确保所有信号路径满足时序要求;同时进行设计规则检查(DRC)和版图与原理图一致性检查(LVS),确保版图符合晶圆厂的制造工艺规则且与网表逻辑一致。

- 版图交付:最终生成符合要求的GDSII格式版图文件,交付给晶圆厂进行掩膜制作与流片生产。

三、命名法与设计的交汇:协同与映射

集成电路的型号命名与其设计过程密切相关。设计阶段确定的芯片功能、性能等级和采用的工艺技术,最终会凝结在型号名称中。例如,一个采用先进28纳米工艺、面向低功耗移动应用设计的处理器,其型号后缀可能包含“LP”(低功耗)标识;而一个经过汽车级可靠性设计验证的芯片,其型号中可能体现“Q”或“AEC-Q100”等车规认证信息。

反之,型号命名法也为设计提供了目标和约束。设计师在项目伊始,就需要明确未来芯片的型号定位,这直接指导了架构选型、IP核复用、工艺库选择以及最终的测试与封装方案。

###

半导体集成电路的型号命名法与设计流程,是技术工程化与产品管理智慧的集中体现。命名法是对设计成果的标准化凝练与市场语言翻译,而设计流程则是实现这一成果的科学方法与技术路径。二者相辅相成,共同推动着芯片性能的不断提升与应用领域的持续拓展,支撑着整个数字世界的飞速演进。理解这套体系,对于深入参与半导体产业的研发、生产、销售乃至应用环节,都具有重要意义。